使用LDO和PLD实现电源启用和禁用功能

许多系统需要通过控制线或在施加输入电源时启用和禁用。虽然小型微控制器 (MCU) 可以实现启用/禁用功能,但您仍然需要为其编写、维护和烧录代码。许多使用片上系统 (SoC) 的设计在该芯片内都有一个 MCU;添加另一个是多余的。此外,SoC 中的 MCU 不够低功耗,无法保持始终开启并提供启用控制器功能。

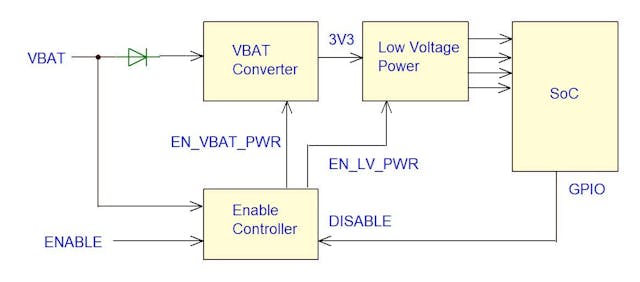

本文讨论了一种低成本、低功耗的使能控制器硬件解决方案,该解决方案使用低压差线性稳压器 (LDO) 和可编程逻辑器件 (PLD),仅消耗微安级电流。PLD 预编程了实现使能控制器决策功能所需的逻辑。图 1 显示了建议的解决方案;其电源通常用于为 SoC 供电的汽车系统。

图1. 说明 SoC、电源和使能控制器的基本系统图。启用控制器解决方案

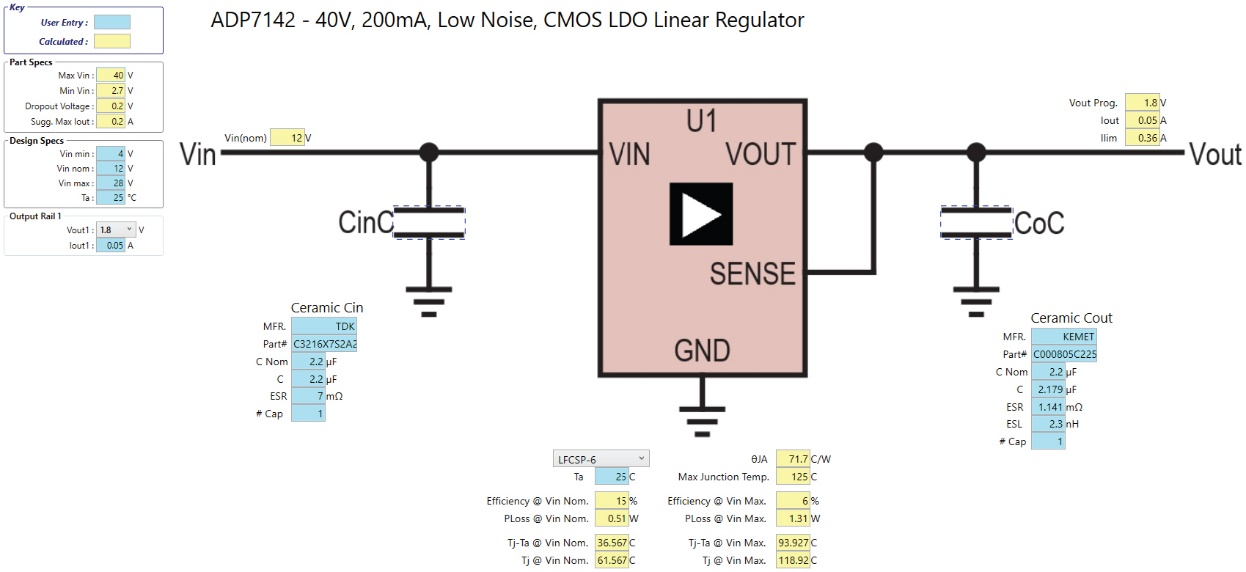

该解决方案采用 TPS7B85-Q1 电池断续 LDO1 和 TPLD801-Q1 PLD2(图 2)。TPS7B85-Q1 中的功能在此应用中特别有用:

基本 LDO 功能从高达 40V 的电池电压 (VBAT) 提供固定的 3.3V 或 5V 输出电压 (VOUT)。此 VOUT 为 TPLD801-Q1 供电。

具有引脚可编程延迟的电源就绪 (PG) 输出。当施加 VBAT 时,LDO 上电。当 LDO VOUT 达到稳压时, PG 在 DELAY 引脚上的电容器编程的延迟后变为高电平。TPLD801-Q1 使用上升的 PG 信号来检测和锁存 VBAT (FIRST_EN) 的初始应用以启用系统。

如果非专用 SENSE 比较器的感应输入引脚(SI 引脚)分别高于或低于 1.21 V 内部电压基准 (VREF),则提供逻辑高电平或低电平检测输出(SO 引脚)。SI 引脚的最大电压为 40 V,无论 LDO VIN 是否通电。对于阻断负电压,您可以使用二极管 D2。比较器测试ENABLE_IN信号的幅度是否高于某个电压阈值。如果是,则允许 signal 传递到 TPLD801-Q1 的 enable input。该电压阈值可通过 R4 和 R5 进行调节。

一个精密使能 (EN) 引脚。精密使能功能(与逻辑电平使能相反)未记录在 TPS7B85-Q1 数据表中,但 EN 引脚连接到具有 1.32 VV REF 阈值(上升)和 100 mV 迟滞的比较器。它允许使用从 VBAT 到 EN 再到接地的电阻分压器 (R2, R3) 来设置精确的 VBAT 启动电压。使用精密使能可确保 LDO 的输出不会随着 VBAT (具有未知的斜坡速率)而斜坡上升,而是等到 VBAT 高于设定的启动电压后再打开 LDO。在这种情况下,VOUT 在大约 240 μs 内上升,与 VBAT 斜坡速率无关。从所示的电阻值来看,LDO 的 VBAT 启动电压约为 6.5 V,但可通过 R2 和 R3 进行调节。VOUT 的斜坡速率很重要,因为 TPLD801-Q1 的最大(最慢)允许 VCC 斜坡速率为 0.25 V/ms。

图2. 这是使能控制器的原理图。

泄放电阻 R1 在掉电期间对 LDO (C1) 的输出电容器放电。TPS7B85-Q1 的 PG 和 SO 引脚上具有 30kΩ 内部上拉电阻器。PG delay 的长度是一个选择问题。CDELAY = 4.7 nF 的延迟约为 4 ms(图 2)。

TPLD801-Q1 的一些设计说明

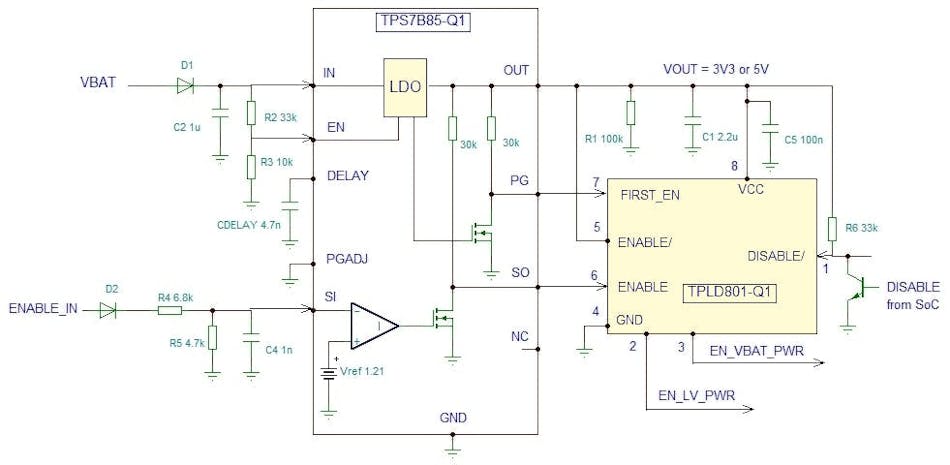

TPLD801-Q1 是一款符合汽车标准的 PLD,集成了触发器、计数器、延迟、逻辑门和 25 kHz 或 2 MHz 振荡器等逻辑模块,以及分频器和流水线延迟。TI 的 InterConnect Studio 设计工具可以图形方式设计和仿真逻辑设计。

您还可以使用 TPLD801 评估模块和 TPLD 编程器套件将逻辑设计永久编程到一次性可编程存储器中,或将设计临时编程到易失性寄存器中。

TPLD801-Q1 logic design 的核心是一个配置为 latch (ENABLE LATCH) 的 D 型 flip-flop,因此 rising clock edge 锁存一个 logic-high output。只有 reset input 可以重置 latch。锁存器输出进入两条单独的延迟线,每条延迟线设置为大约 15 ms。当锁存器输出变为高电平时,EN_VBAT_PWR信号立即变为高电平并启用前端电源。

为了留出时间让前端首先上电,EN_LV_PWR信号在大约 15 毫秒后变为高电平,并使能为 SoC 和系统其余部分供电的电源。

可以通过两种方式为 ENABLE LATCH 提供 rising edge 的时钟:

在第一个使能事件中,在 LDO 的 PG 输出上产生一个上升沿。

使用 ENABLE 信号从 TPS7B85-Q1 的 SO 输出传递到 PLD,并且 PLD 测量的内容比预编程的持续时间长。或者,如果您需要不同的应用程序,您可以使用反向 ENABLE/ 信号;但如果不使用,它就会被绑得很高。

在第二种情况下,为了抑制杂散噪声信号,PLD 通过延迟线来测量输入的 ENABLE 信号是否足够长,该延迟线由 PLD 的内部 25 kHz 除频振荡器计时。25 kHz 振荡器的功耗非常低,功耗为 8.2 μA。

延迟线计数 94 的总延迟约为 15 毫秒,但您可以根据应用程序的要求将此时间设置为不同的持续时间。如果在此延迟期间和之后输入的 ENABLE 信号仍然存在,则延迟线的输出变为高电平,这会为 ENABLE LATCH 的 clock 提供上升沿并锁存一个逻辑高电平。如果输入的 ENABLE 信号在整个时间内都不存在,则 delay counter 将重置,并且不会发生 latch 的上升沿。

当电子控制单元需要断电时,SoC 的 MCU 通过通用输入/输出发出上升沿。该 DISABLE 信号连接到图 1 所示的漏极开路晶体管,并下拉 PLD 的 DISABLE/ 引脚以重置 ENABLE LATCH。ENABLE LATCH 复位后, EN_LV_PWR 输出立即变为低电平;大约 15 ms 后,EN_VBAT_PWR 输出变为低电平。

这个 15 毫秒的延迟使低压电源轨能够在前端电源被禁用之前按照 SoC 要求的正确顺序进行降序。EN_VBAT_PWR 和 EN_LV_PWR 上升或下降之间的延迟时间可以通过更改延迟线的数量来配置。

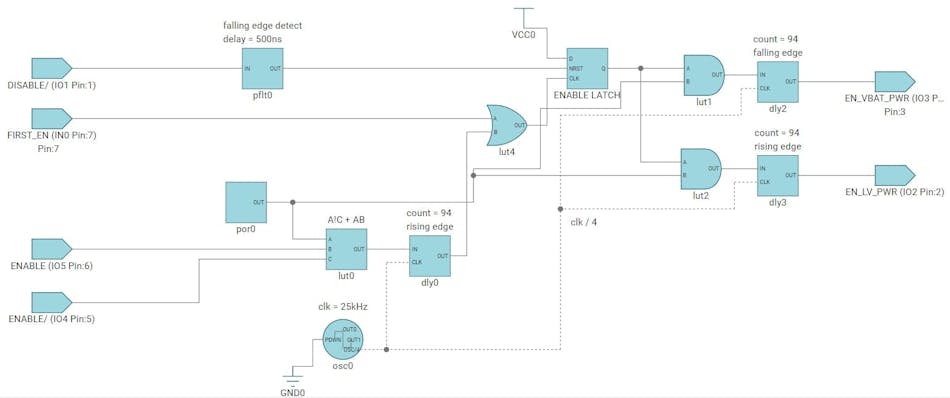

选择 PLD 输入作为施密特触发器输入,为驱动到它们的 logic signals 需要多快转换提供了余地。两个使能输出信号配置为推挽式。(如果使用开漏,则此配置会在上电时产生毛刺,因为在 TPLD801-Q1 的一次性可编程存储器 OTP 加载并将输出配置为开漏之前,开漏输出被上拉电阻器暂时拉高。即使使用推挽式,在 OTP 存储器加载之前,输出也是高阻抗的;因此,您可能需要外部 pull-down 电阻器。图 3 显示了整体 PLD 设计。

图3. 此图显示了 TPLD801-Q1 的内部结构。PLD/LDO 组合的基准测试结果

图3. 此图显示了 TPLD801-Q1 的内部结构。PLD/LDO 组合的基准测试结果

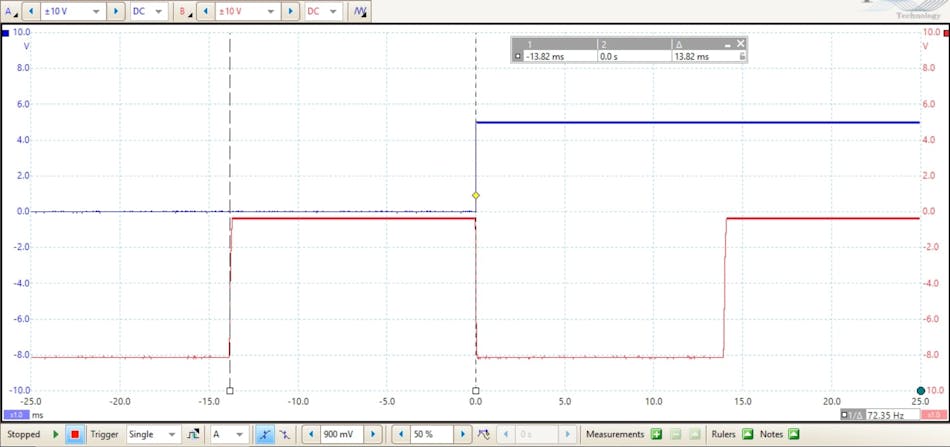

图 4 显示了施加到使能控制器的 18 V ENABLE_IN信号,该信号的幅度肯定使 TPS7B85-Q1 比较器能够将其传递到 PLD。该信号还具有足够的持续时间,以便 PLD 验证检测。ENABLE LATCH 响应此 ENABLE_IN 信号而锁定为高电平,即使 ENABLE_IN 被切换,它也保持高电平。

图4. 将 18 V ENABLE_IN信号施加到使能控制器,该信号肯定具有允许 TPS7B85-Q1 比较器将其传递到 PLD 的幅度。用于 18 V ENABLE_IN信号的 TPS7B85-Q1 SI 引脚电压以红色显示,ENABLE LATCH 内部 PLD 电压以蓝色显示。

图4. 将 18 V ENABLE_IN信号施加到使能控制器,该信号肯定具有允许 TPS7B85-Q1 比较器将其传递到 PLD 的幅度。用于 18 V ENABLE_IN信号的 TPS7B85-Q1 SI 引脚电压以红色显示,ENABLE LATCH 内部 PLD 电压以蓝色显示。

在另一个极端情况下,可以成功地对低幅度的 3.4 V 信号重复此测试。或者,您可以对持续时间短、振幅低的 ENABLE_IN 信号重复测试,或者两者兼而有之,这些信号的持续时间或振幅不足以触发 ENABLE LATCH 为高电平。

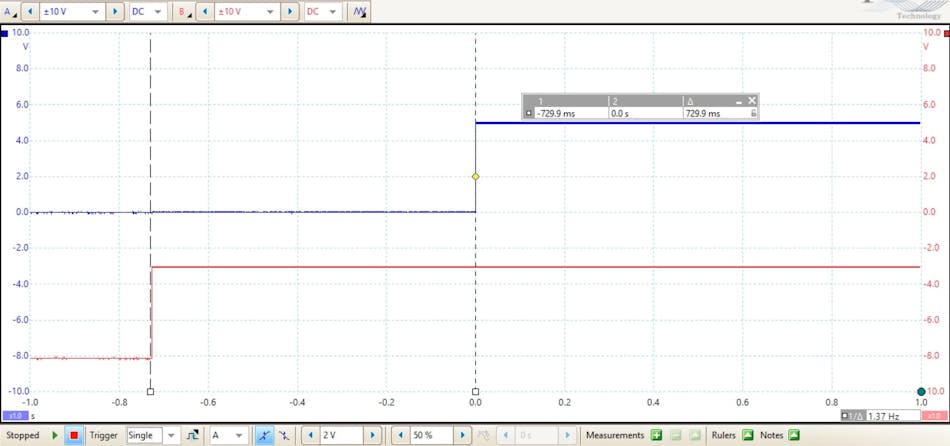

图 5 显示了首次将输入电源施加到 LDO 时的电路行为。当 LDO 调节时,PG 引脚变为高电平,经过延迟 (由 CDELAY 设置) 后,PLD 检测到第一个上电事件,并且 ENABLE LATCH 锁存为高电平。(此测试使用评估板的默认 1 μF CDELAY 电容器,其延迟要长得多。

图5. 此图显示了首次将输入电源施加到 LDO 时的电路行为。TPS7B85-Q1 PG 引脚电压在首次上电时显示为红色,ENABLE LATCH 电压显示为蓝色。

图5. 此图显示了首次将输入电源施加到 LDO 时的电路行为。TPS7B85-Q1 PG 引脚电压在首次上电时显示为红色,ENABLE LATCH 电压显示为蓝色。

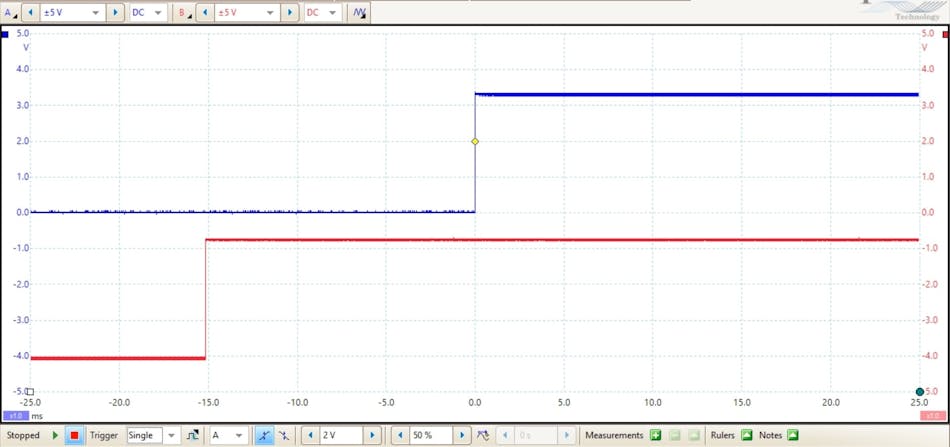

PLD 的实际输出如图 6 所示,包括上电序列期间大约 15 ms 的延迟。

图6. 这些是 PLD 的实际输出,包括上电序列期间大约 15 ms 的延迟。EN_VBAT_PWR 输出以红色显示,EN_LV_PWR 的 PLD 输出以蓝色显示。

图6. 这些是 PLD 的实际输出,包括上电序列期间大约 15 ms 的延迟。EN_VBAT_PWR 输出以红色显示,EN_LV_PWR 的 PLD 输出以蓝色显示。

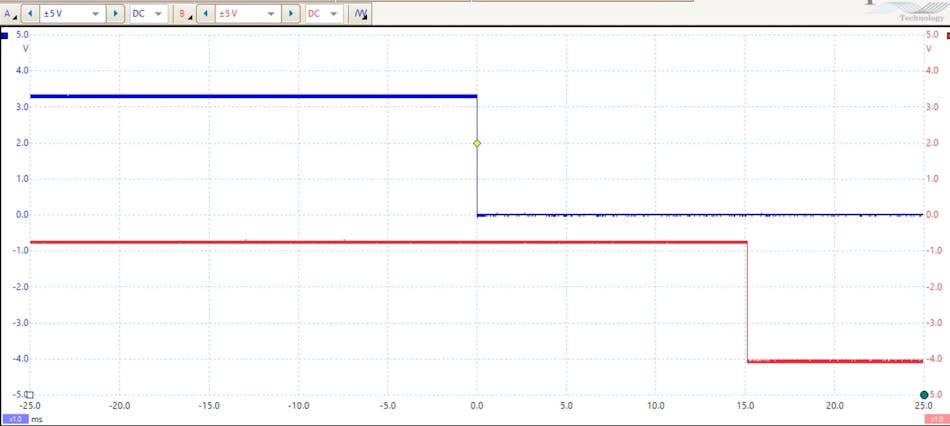

图 7 显示了 DISABLE 事件期间的 PLD 输出,描述了 15 ms 的延迟。

图7. 这将突出显示睡眠行为,显示 EN_LV_PWR(蓝色)变为低电平,然后是 EN_VBAT_PWR 信号(红色)。

图7. 这将突出显示睡眠行为,显示 EN_LV_PWR(蓝色)变为低电平,然后是 EN_VBAT_PWR 信号(红色)。

为什么 PLD/LDO 组合优于微控制器

这种基于硬件的低成本、低功耗解决方案用于处理电源启用和禁用功能,无需外部 MCU,并且可以进一步定制。您还可以选择订购预编程了 logic design 的定制 PLD。

预编程的 PLD 避免了为 MCU 编写和维护固件的时间和成本。此外,它避免了在生产环境中对 MCU 进行编程。具有预编程 PLD 的这些省时功能以及 TPLD801-Q1 和 TPS7B85-Q1 硬件解决方案成本低的事实节省了整体系统费用。

TPLD801-Q1 采用 1.6 × 2.1 mm 的小封装,TPS7B85-Q1 采用 3 × 3 mm 封装,可节省整个印刷电路板布局的空间。这对于印刷电路板设计人员很有帮助,因为他们经常面临必须在同一电路板区域内安装更多功能的任务。